220von tiếp tục chia sẽ toàn bộ project điều khiển góc quay 10 động cơ servo từ xa bằng 10 biến trở dùng module NRF24L01 và IC vi điều khiển PIC16F886

Khoảng cách khi dùng module này là 10m trở lại , nếu dùng module có PA công xuất cao hơn thì khoản cách thu phát lên đến 500m

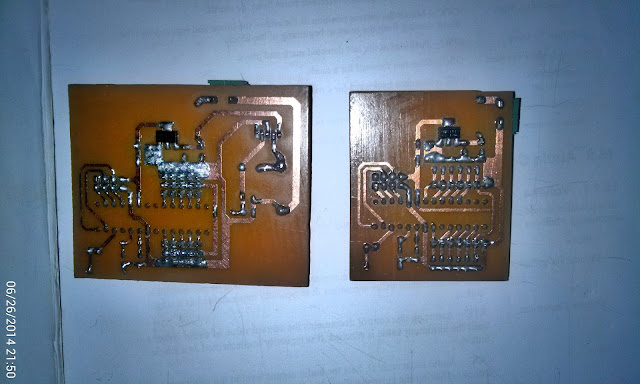

Ảnh chụp mạch thực tế :

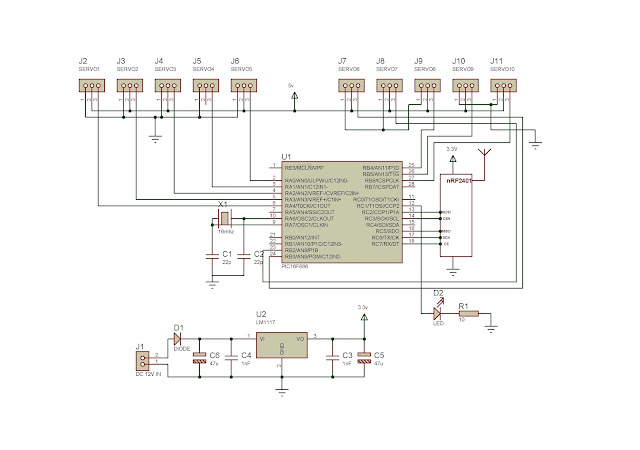

Sơ đồ mạch thu và phát :

|

| sơ đồ mạch thu |

|

| sơ đồ mạch phát |

Video test mạch :

Code C của mạch phát :

////////////////////////////////////////////////

Blog : 220von.blogspot.com

Email : 220von.com@gmail.com

///////////////////////////////////////////////

#include <16F886.h>

#device adc=8

#FUSES NOWDT //No Watch Dog Timer

#FUSES HS //High speed Osc (> 4mhz for PCM/PCH) (>10mhz for PCD)

#FUSES NOPUT //No Power Up Timer

#FUSES NOMCLR //Master Clear pin used for I/O

#FUSES NOPROTECT //Code not protected from reading

#FUSES NOCPD //No EE protection

#FUSES NOBROWNOUT //No brownout reset

#FUSES IESO //Internal External Switch Over mode enabled

#FUSES FCMEN //Fail-safe clock monitor enabled

#FUSES NOLVP //No low voltage prgming, B3(PIC16) or B5(PIC18) used for I/O

#FUSES NODEBUG //No Debug mode for ICD

#FUSES NOWRT //Program memory not write protected

#FUSES BORV40 //Brownout reset at 4.0V

#FUSES RESERVED //Used to set the reserved FUSE bits

#use delay(clock=16000000)

extern unsigned char TxBuf[32];

//*********************************************NRF24L01*************************************

#define TX_ADR_WIDTH 5 // 5 uints TX address width

#define RX_ADR_WIDTH 5 // 5 uints RX address width

#define TX_PLOAD_WIDTH 10 // 32 uints TX payload

#define RX_PLOAD_WIDTH 10 // 32 uints TX payload

//***************************************NRF24L01*******************************************************

#define READ_REG 0x00 //

#define WRITE_REG 0x20 //

#define RD_RX_PLOAD 0x61 //

#define WR_TX_PLOAD 0xA0 //

#define FLUSH_TX 0xE1 //

#define FLUSH_RX 0xE2 //

#define REUSE_TX_PL 0xE3 //

#define NOP 0xFF //

//*************************************SPI(nRF24L01)·****************************************************

#define CONFIG 0x00 //

#define EN_AA 0x01 //

#define EN_RXADDR 0x02 //

#define SETUP_AW 0x03 //

#define SETUP_RETR 0x04 //

#define RF_CH 0x05 //

#define RF_SETUP 0x06 //

#define STATUS 0x07 //

#define OBSERVE_TX 0x08 // ·

#define CD 0x09 //

#define RX_ADDR_P0 0x0A //

#define RX_ADDR_P1 0x0B //

#define RX_ADDR_P2 0x0C //

#define RX_ADDR_P3 0x0D //

#define RX_ADDR_P4 0x0E //

#define RX_ADDR_P5 0x0F //

#define TX_ADDR 0x10 //

#define RX_PW_P0 0x11 //

#define RX_PW_P1 0x12 //

#define RX_PW_P2 0x13 //

#define RX_PW_P3 0x14 //

#define RX_PW_P4 0x15 //

#define RX_PW_P5 0x16 //

#define FIFO_STATUS 0x17 //

//**************************************************************************************

#define CE PIN_C7

#define CSN PIN_C3

#define SCK PIN_C6

#define MOSI PIN_C2

#define MISO PIN_C5

#define LED PIN_C1

//**************************************************************************************

unsigned char TxBuf[10]=

{

0x01,0x02,0x03,0x4,0x05,0x06,0x07,0x08,

0x09,0x10,

};

unsigned char TX_ADDRESS[TX_ADR_WIDTH]= {0x34,0x43,0x10,0x10,0x01}; //

unsigned char RX_ADDRESS[RX_ADR_WIDTH]= {0x34,0x43,0x10,0x10,0x01}; //

//****************************************************************************************

void init_NRF24L01(void);

unsigned char SPI_RW(unsigned char Buff);

unsigned char SPI_Read_reg(unsigned char reg);

unsigned char SPI_RW_Reg(unsigned char reg, unsigned char value);

unsigned char SPI_Read_Buf(unsigned char reg, unsigned char *pBuf, unsigned char uchars);

unsigned char SPI_Write_Buf(unsigned char reg, unsigned char *pBuf, unsigned uchars);

void SetRX_Mode(void);

void SetTX_Mode(void);

unsigned char nRF24L01_RxPacket(unsigned char* rx_buf);

void nRF24L01_TxPacket(unsigned char * tx_buf);

// -------------------------------------------------------

void main()

{

set_tris_c(0b00100000);

output_c(0x00);

char RxBuf[10];

setup_adc_ports(sAN0|sAN1|sAN2|sAN3|sAN4|sAN8|sAN9|sAN10|sAN11|sAN12|VSS_VDD);

setup_adc(ADC_CLOCK_DIV_2);

delay_ms(1000);

init_NRF24L01();

SetTX_Mode();

char sv1,sv2,sv3,sv4,sv5;

char sv6,sv7,sv8,sv9,sv10;

while(true)

{

set_adc_channel(0);

delay_us(10);

sv1 = 6 + read_adc()/13;

delay_us(10);

RxBuf[0] = sv1;

delay_us(10);

set_adc_channel(1);

delay_us(10);

sv2 = 6 + read_adc()/13;

delay_us(10);

RxBuf[1] = sv2;

delay_us(10);

set_adc_channel(2);

delay_us(10);

sv3 = 6 + read_adc()/13;

delay_us(10);

RxBuf[2] = sv3;

delay_us(10);

set_adc_channel(3);

delay_us(10);

sv4 = 6 + read_adc()/13;

delay_us(10);

RxBuf[3] = sv4;

delay_us(10);

set_adc_channel(4);

delay_us(10);

sv5 = 6 + read_adc()/13;

delay_us(10);

RxBuf[4] = sv5;

delay_us(10);

/////////////////////////////////////////

set_adc_channel(11);

delay_us(10);

sv6 = 6 + read_adc()/13;

delay_us(10);

RxBuf[5] = sv6;

delay_us(10);

set_adc_channel(9);

delay_us(10);

sv7 = 6 + read_adc()/13;

delay_us(10);

RxBuf[6] = sv7;

delay_us(10);

set_adc_channel(8);

delay_us(10);

sv8 = 6 + read_adc()/13;

delay_us(10);

RxBuf[7] = sv8;

delay_us(10);

set_adc_channel(10);

delay_us(10);

sv9 = 6 + read_adc()/13;

delay_us(10);

RxBuf[8] = sv9;

delay_us(10);

set_adc_channel(12);

delay_us(10);

sv10 = 6 + read_adc()/13;

delay_us(10);

RxBuf[9] = sv10;

delay_us(10);

/////////////////////////////////////////////////////////////

// SetTX_Mode();

// delay_ms(10);

nRF24L01_TxPacket(RxBuf); // Transmit Tx buffer data

SPI_RW_Reg(WRITE_REG+STATUS,0XFF); // Clear Bit Send

output_toggle(LED);

delay_ms(1);

}

}

//*NRF24L01

//***************************************************************************************/

void init_NRF24L01(void)

{

delay_us(100);

output_low(CE); // chip enable

output_high(CSN); // Spi disable

output_low(SCK); // Spi clock line init high

SPI_Write_Buf(WRITE_REG + TX_ADDR, TX_ADDRESS, TX_ADR_WIDTH); //

SPI_Write_Buf(WRITE_REG + RX_ADDR_P0, RX_ADDRESS, RX_ADR_WIDTH); //

SPI_RW_Reg(WRITE_REG + EN_AA, 0x01); // EN P0, 2-->P1

SPI_RW_Reg(WRITE_REG + EN_RXADDR, 0x01); //Enable data P0

SPI_RW_Reg(WRITE_REG + RF_CH, 0); // Chanel 0 RF = 2400 + RF_CH* (1or 2 M)

SPI_RW_Reg(WRITE_REG + RX_PW_P0, RX_PLOAD_WIDTH); // Do rong data truyen 32 byte

SPI_RW_Reg(WRITE_REG + RF_SETUP, 0x07); // 1M, 0dbm

SPI_RW_Reg(WRITE_REG + CONFIG, 0x0e); // Enable CRC, 2 byte CRC, Send

}

/****************************************************************************************************/

//unsigned char SPI_RW(unsigned char Buff)

//NRF24L01

/****************************************************************************************************/

unsigned char SPI_RW(unsigned char Buff)

{

unsigned char bit_ctr;

for(bit_ctr=0;bit_ctr<8;bit_ctr++) // output 8-bit

{

if(Buff & 0x80) output_high(MOSI) ; // output 'uchar', MSB to MOSI

else output_low(MOSI);

delay_us(5);

Buff = (Buff << 1); // shift next bit into MSB..

output_high(SCK); // Set SCK high..

delay_us(5);

if((input(MISO))==1)Buff |= 0x01; // capture current MISO bit

output_low(SCK); // ..then set SCK low again

}

return(Buff); // return read uchar

}

/****************************************************************************************************/

//unsigned char SPI_Read(unsigned char reg)

//NRF24L01

/****************************************************************************************************/

unsigned char SPI_Read_reg(unsigned char reg)

{

unsigned char reg_val=0;

output_low(CSN); // CSN low, initialize SPI communication...

SPI_RW(reg); // Select register to read from..

reg_val = SPI_RW(0); // ..then read registervalue

output_high(CSN); // CSN high, terminate SPI communication

return (reg_val); // return register value

}

/****************************************************************************************************/

//unsigned char SPI_RW_Reg(unsigned char reg, unsigned char value)

/****************************************************************************************************/

unsigned char SPI_RW_Reg(unsigned char reg,unsigned char value)

{

unsigned char status1;

output_low(CSN); // CSN low, init SPI transaction

status1 = SPI_RW(reg); // select register

SPI_RW(value); // ..and write value to it..

output_high(CSN); // CSN high again

return(status1); // return nRF24L01 status uchar

}

/****************************************************************************************************/

//unsigned char SPI_Read_Buf(unsigned char reg, unsigned char *pBuf, unsigned char uchars)

//

/****************************************************************************************************/

unsigned char SPI_Read_Buf(unsigned char reg,unsigned char *pBuf,unsigned char uchars)

{

unsigned char status1,uchar_ctr;

output_low(CSN); // Set CSN low, init SPI tranaction

status1 = SPI_RW(reg); // Select register to write to and read status uchar

for(uchar_ctr=0;uchar_ctr<uchars;uchar_ctr++) pBuf[uchar_ctr] = SPI_RW(0); //

output_high(CSN);

return(status1); // return nRF24L01 status uchar

}

/*********************************************************************************************************/

//uint SPI_Write_Buf(uchar reg, uchar *pBuf, uchar uchars)

/*****************************************************************************************************/

unsigned char SPI_Write_Buf(unsigned char reg,unsigned char *pBuf,unsigned char uchars)

{

unsigned char status1,uchar_ctr;

output_low(CSN); //SPI

status1 = SPI_RW(reg);

for(uchar_ctr=0; uchar_ctr<uchars; uchar_ctr++) //

SPI_RW(*pBuf++);

output_high(CSN); //SPI

return(status1); //

}

/****************************************************************************************************/

//void SetRX_Mode(void)

//

/****************************************************************************************************/

void SetRX_Mode(void)

{

output_low(CE);

SPI_RW_Reg(WRITE_REG + CONFIG, 0x0f); // Enable CRC, 2 byte CRC, Recive

output_high(CE);

delay_us(130); //

}

/****************************************************************************************************/

//void SetTX_Mode(void)

//

/****************************************************************************************************/

void SetTX_Mode(void)

{

output_low(CE);

SPI_RW_Reg(WRITE_REG + CONFIG, 0x0e); // Enable CRC, 2 byte CRC, Send

output_high(CE);

delay_us(130); //

}

/******************************************************************************************************/

//unsigned char nRF24L01_RxPacket(unsigned char* rx_buf)

/******************************************************************************************************/

unsigned char nRF24L01_RxPacket(unsigned char* rx_buf)

{

unsigned char revale=0;

unsigned char sta;

//if(RX_DR) // Data in RX FIFO

sta=SPI_Read_reg(STATUS); // Read Status

if(sta&0x40) // Data in RX FIFO

{

output_low(CE); //SPI

SPI_Read_Buf(RD_RX_PLOAD,rx_buf,TX_PLOAD_WIDTH);// read receive payload from RX_FIFO buffer

revale =1;

}

SPI_RW_Reg(WRITE_REG+STATUS,sta);

return(revale);

}

/***********************************************************************************************************/

//void nRF24L01_TxPacket(unsigned char * tx_buf)

//

/**********************************************************************************************************/

void nRF24L01_TxPacket(unsigned char * tx_buf)

{

output_low(CE);

SPI_Write_Buf(WRITE_REG + RX_ADDR_P0, TX_ADDRESS, TX_ADR_WIDTH); // Send Address

SPI_Write_Buf(WR_TX_PLOAD, tx_buf, TX_PLOAD_WIDTH); //send data

SPI_RW_Reg(WRITE_REG + CONFIG, 0x0e); // Send Out

output_high(CE);

}

// --------------------END OF FILE------------------------

// -------------------------------------------------------

Code C mạch thu :

////////////////////////////////////////////////

Blog : 220von.blogspot.com

Email : 220von.com@gmail.com

///////////////////////////////////////////////

#include <16F886.h>

#device adc=8

#FUSES NOWDT //No Watch Dog Timer

#FUSES HS //High speed Osc (> 4mhz for PCM/PCH) (>10mhz for PCD)

#FUSES NOPUT //No Power Up Timer

#FUSES NOMCLR //Master Clear pin used for I/O

#FUSES NOPROTECT //Code not protected from reading

#FUSES NOCPD //No EE protection

#FUSES NOBROWNOUT //No brownout reset

#FUSES IESO //Internal External Switch Over mode enabled

#FUSES FCMEN //Fail-safe clock monitor enabled

#FUSES NOLVP //No low voltage prgming, B3(PIC16) or B5(PIC18) used for I/O

#FUSES NODEBUG //No Debug mode for ICD

#FUSES NOWRT //Program memory not write protected

#FUSES BORV40 //Brownout reset at 4.0V

#FUSES RESERVED //Used to set the reserved FUSE bits

#use delay(clock=16000000)

//************************************************************************************************8

extern unsigned char TxBuf[32];

//*********************************************NRF24L01*************************************

#define TX_ADR_WIDTH 5 // 5 uints TX address width

#define RX_ADR_WIDTH 5 // 5 uints RX address width

#define TX_PLOAD_WIDTH 10 // 32 uints TX payload

#define RX_PLOAD_WIDTH 10 // 32 uints TX payload

//***************************************NRF24L01*******************************************************

#define READ_REG 0x00 //

#define WRITE_REG 0x20 //

#define RD_RX_PLOAD 0x61 //

#define WR_TX_PLOAD 0xA0 //

#define FLUSH_TX 0xE1 //

#define FLUSH_RX 0xE2 //

#define REUSE_TX_PL 0xE3 //

#define NOP 0xFF //

//*************************************SPI(nRF24L01)·****************************************************

#define CONFIG 0x00 //

#define EN_AA 0x01 //

#define EN_RXADDR 0x02 //

#define SETUP_AW 0x03 //

#define SETUP_RETR 0x04 //

#define RF_CH 0x05 //

#define RF_SETUP 0x06 //

#define STATUS 0x07 //

#define OBSERVE_TX 0x08 // ·

#define CD 0x09 //

#define RX_ADDR_P0 0x0A //

#define RX_ADDR_P1 0x0B //

#define RX_ADDR_P2 0x0C //

#define RX_ADDR_P3 0x0D //

#define RX_ADDR_P4 0x0E //

#define RX_ADDR_P5 0x0F //

#define TX_ADDR 0x10 //

#define RX_PW_P0 0x11 //

#define RX_PW_P1 0x12 //

#define RX_PW_P2 0x13 //

#define RX_PW_P3 0x14 //

#define RX_PW_P4 0x15 //

#define RX_PW_P5 0x16 //

#define FIFO_STATUS 0x17 //

//**************************************************************************************

#define CE PIN_C7

#define CSN PIN_C3

#define SCK PIN_C6

#define MOSI PIN_C2

#define MISO PIN_C5

#define LED PIN_C1

//**************************************************************************************

unsigned char TxBuf[10]=

{

0x01,0x02,0x03,0x4,0x05,0x06,0x07,0x08,

0x09,0x10,

};

unsigned char TX_ADDRESS[TX_ADR_WIDTH]= {0x34,0x43,0x10,0x10,0x01}; //

unsigned char RX_ADDRESS[RX_ADR_WIDTH]= {0x34,0x43,0x10,0x10,0x01}; //

//****************************************************************************************

void init_NRF24L01(void);

unsigned char SPI_RW(unsigned char Buff);

unsigned char SPI_Read_reg(unsigned char reg);

unsigned char SPI_RW_Reg(unsigned char reg, unsigned char value);

unsigned char SPI_Read_Buf(unsigned char reg, unsigned char *pBuf, unsigned char uchars);

unsigned char SPI_Write_Buf(unsigned char reg, unsigned char *pBuf, unsigned uchars);

void SetRX_Mode(void);

void SetTX_Mode(void);

unsigned char nRF24L01_RxPacket(unsigned char* rx_buf);

void nRF24L01_TxPacket(unsigned char * tx_buf);

char count=0;

char sv1=15,sv2=15,sv3=15,sv4=15,sv5=15;

char sv6=15,sv7=15,sv8=15,sv9=15,sv10=15;

// -------------------------------------------------------

#int_TIMER0

void TIMER0_isr(void)

{

set_timer0(168);

count++;

if(count>=200)

{

output_b(0xFF);

output_a(0xFF);

count=0;

}

if(count>=sv1)output_low(PIN_A0);

if(count>=sv2)output_low(PIN_A1);

if(count>=sv3)output_low(PIN_A2);

if(count>=sv4)output_low(PIN_A3);

if(count>=sv5)output_low(PIN_A4);

/////////////////////////////////

if(count>=sv6)output_low(PIN_B6);

if(count>=sv7)output_low(PIN_B5);

if(count>=sv8)output_low(PIN_B4);

if(count>=sv9)output_low(PIN_B3);

if(count>=sv10)output_low(PIN_B2);

}

void main()

{

set_tris_c(0b00100000);

set_tris_b(0x00);

set_tris_a(0x00);

output_a(0x00);

output_b(0x00);

output_c(0x00);

delay_ms(1000);

setup_timer_0(RTCC_INTERNAL|RTCC_DIV_4);

set_timer0(164);

setup_timer_1(T1_DISABLED);

setup_timer_2(T2_DISABLED,0,1);

char RxBuf[10];

output_low(LED);

init_NRF24L01();

SetRX_Mode();

enable_interrupts(INT_TIMER0);

enable_interrupts(GLOBAL);

char st=0;

while(true)

{

if(nRF24L01_RxPacket(RxBuf)==1) // Neu nhan duoc du lieu

{

sv1=RxBuf[0];

sv2=RxBuf[1];

sv3=RxBuf[2];

sv4=RxBuf[3];

sv5=RxBuf[4];

////////////

sv6=RxBuf[5];

sv7=RxBuf[6];

sv8=RxBuf[7];

sv9=RxBuf[8];

sv10=RxBuf[9];

output_toggle(LED);

SetRX_Mode();

}

}

}

//*NRF24L01

//***************************************************************************************/

void init_NRF24L01(void)

{

delay_us(100);

output_low(CE); // chip enable

output_high(CSN); // Spi disable

output_low(SCK); // Spi clock line init high

SPI_Write_Buf(WRITE_REG + TX_ADDR, TX_ADDRESS, TX_ADR_WIDTH); //

SPI_Write_Buf(WRITE_REG + RX_ADDR_P0, RX_ADDRESS, RX_ADR_WIDTH); //

SPI_RW_Reg(WRITE_REG + EN_AA, 0x01); // EN P0, 2-->P1

SPI_RW_Reg(WRITE_REG + EN_RXADDR, 0x01); //Enable data P0

SPI_RW_Reg(WRITE_REG + RF_CH, 0); // Chanel 0 RF = 2400 + RF_CH* (1or 2 M)

SPI_RW_Reg(WRITE_REG + RX_PW_P0, RX_PLOAD_WIDTH); // Do rong data truyen 32 byte

SPI_RW_Reg(WRITE_REG + RF_SETUP, 0x07); // 1M, 0dbm

SPI_RW_Reg(WRITE_REG + CONFIG, 0x0e); // Enable CRC, 2 byte CRC, Send

}

/****************************************************************************************************/

//unsigned char SPI_RW(unsigned char Buff)

//NRF24L01

/****************************************************************************************************/

unsigned char SPI_RW(unsigned char Buff)

{

unsigned char bit_ctr;

for(bit_ctr=0;bit_ctr<8;bit_ctr++) // output 8-bit

{

if(Buff & 0x80) output_high(MOSI) ; // output 'uchar', MSB to MOSI

else output_low(MOSI);

delay_us(5);

Buff = (Buff << 1); // shift next bit into MSB..

output_high(SCK); // Set SCK high..

delay_us(5);

if((input(MISO))==1)Buff |= 0x01; // capture current MISO bit

output_low(SCK); // ..then set SCK low again

}

return(Buff); // return read uchar

}

/****************************************************************************************************/

//unsigned char SPI_Read(unsigned char reg)

//NRF24L01

/****************************************************************************************************/

unsigned char SPI_Read_reg(unsigned char reg)

{

unsigned char reg_val;

output_low(CSN); // CSN low, initialize SPI communication...

SPI_RW(reg); // Select register to read from..

reg_val = SPI_RW(0); // ..then read registervalue

output_high(CSN); // CSN high, terminate SPI communication

return (reg_val); // return register value

}

/****************************************************************************************************/

//unsigned char SPI_RW_Reg(unsigned char reg, unsigned char value)

/****************************************************************************************************/

unsigned char SPI_RW_Reg(unsigned char reg,unsigned char value)

{

unsigned char status1;

output_low(CSN); // CSN low, init SPI transaction

status1 = SPI_RW(reg); // select register

SPI_RW(value); // ..and write value to it..

output_high(CSN); // CSN high again

return(status1); // return nRF24L01 status uchar

}

/****************************************************************************************************/

//unsigned char SPI_Read_Buf(unsigned char reg, unsigned char *pBuf, unsigned char uchars)

//

/****************************************************************************************************/

unsigned char SPI_Read_Buf(unsigned char reg,unsigned char *pBuf,unsigned char uchars)

{

unsigned char status1,uchar_ctr;

output_low(CSN); // Set CSN low, init SPI tranaction

status1 = SPI_RW(reg); // Select register to write to and read status uchar

for(uchar_ctr=0;uchar_ctr<uchars;uchar_ctr++) pBuf[uchar_ctr] = SPI_RW(0); //

output_high(CSN);

return(status1); // return nRF24L01 status uchar

}

/*********************************************************************************************************/

//uint SPI_Write_Buf(uchar reg, uchar *pBuf, uchar uchars)

/*****************************************************************************************************/

unsigned char SPI_Write_Buf(unsigned char reg,unsigned char *pBuf,unsigned char uchars)

{

unsigned char status1,uchar_ctr;

output_low(CSN); //SPI

status1 = SPI_RW(reg);

for(uchar_ctr=0; uchar_ctr<uchars; uchar_ctr++) //

SPI_RW(*pBuf++);

output_high(CSN); //SPI

return(status1); //

}

/****************************************************************************************************/

//void SetRX_Mode(void)

//

/****************************************************************************************************/

void SetRX_Mode(void)

{

output_low(CE);

SPI_RW_Reg(WRITE_REG + CONFIG, 0x0f); // Enable CRC, 2 byte CRC, Recive

output_high(CE);

delay_us(130); //

}

/****************************************************************************************************/

//void SetTX_Mode(void)

//

/****************************************************************************************************/

void SetTX_Mode(void)

{

output_low(CE);

SPI_RW_Reg(WRITE_REG + CONFIG, 0x0e); // Enable CRC, 2 byte CRC, Send

output_high(CE);

delay_us(130); //

}

/******************************************************************************************************/

//unsigned char nRF24L01_RxPacket(unsigned char* rx_buf)

/******************************************************************************************************/

unsigned char nRF24L01_RxPacket(unsigned char* rx_buf)

{

unsigned char revale=0;

unsigned char sta;

//if(RX_DR) // Data in RX FIFO

sta=SPI_Read_reg(STATUS); // Read Status

if(sta&0x40) // Data in RX FIFO

{

output_low(CE); //SPI

SPI_Read_Buf(RD_RX_PLOAD,rx_buf,TX_PLOAD_WIDTH);// read receive payload from RX_FIFO buffer

revale =1;

}

SPI_RW_Reg(WRITE_REG+STATUS,sta);

return(revale);

}

/***********************************************************************************************************/

//void nRF24L01_TxPacket(unsigned char * tx_buf)

//

/**********************************************************************************************************/

void nRF24L01_TxPacket(unsigned char * tx_buf)

{

output_low(CE);

SPI_Write_Buf(WRITE_REG + RX_ADDR_P0, TX_ADDRESS, TX_ADR_WIDTH); // Send Address

SPI_Write_Buf(WR_TX_PLOAD, tx_buf, TX_PLOAD_WIDTH); //send data

SPI_RW_Reg(WRITE_REG + CONFIG, 0x0e); // Send Out

output_high(CE);

}

// --------------------END OF FILE------------------------

// -------------------------------------------------------

Các bạn có thể mở rộng code để điều khiển nhiều động cơ servo hơn

Nếu

các bạn muốn hợp tác với mình để mở rộng chức năng cho ứng dụng này

hoặc chia sẻ ý tưởng ứng dụng vào cuộc sống thì gửi mail cho mình theo

địa chỉ : 220von.com@gmail.com

Hoặc theo dõi trang fan page facebook : https://www.facebook.com/220von/

Mạch test động cơ rc servo:

Hoặc theo dõi trang fan page facebook : https://www.facebook.com/220von/

Mạch test động cơ rc servo:

|

Sản phẩm

Sản phẩm

0 nhận xét:

Đăng nhận xét